### ЛЕВИН Илья Израилевич

Ulefra

## МЕТОДЫ И ПРОГРАММНО-АППАРАТНЫЕ СРЕДСТВА ПАРАЛЛЕЛЬНЫХ СТРУКТУРНО-ПРОЦЕДУРНЫХ ВЫЧИСЛЕНИЙ

Специальности: 05.13.11 — "Математическое и программное обеспечение вычислительных машин, комплексов и компьютерных сетей"

05.13.15 - "Вычислительные машины и системы"

АВТОРЕФЕРАТ диссертации на соискание ученой степени доктора технических наук

Работа выполнена на кафедре "Интеллектуальные многопроцессорные системы" (ИМС) ТРТУ и Южного научного центра РАН, а также в Научно-исследовательском институте многопроцессорных вычислительных систем (НИИ МВС) Государственного образовательного учреждения высшего профессионального образования "Таганрогский государственный радиотехнический университет" (ТРТУ).

НАУЧНЫЕ академик РАН, доктор технических наук, профессор

КОНСУЛЬТАНТЫ: Каляев Анатолий Васильевич,

член-корреспондент РАН, доктор технических наук, профессор Каляев Игорь Анатольевич

ОФИЦИАЛЬНЫЕ член-корреспондент РАН, доктор технических

ОППОНЕНТЫ: наук, профессор

Хорошевский Виктор Гаврилович

доктор технических наук, профессор

Кравченко Павел Павлович

доктор технических наук, старший научный сотрудник

Аграновский Александр Владимирович

ВЕДУЩАЯ ОРГАНИЗАЦИЯ: Институт проблем информатики РАН

(ИПИРАН), г. Москва

Защита состоится "8" октября 2004 г. в <u>1400</u> на заседании диссертационного совета Д 212.259.05 в Таганрогском государственном радиотехническом университете по адресу: 347928, г. Таганрог, ул. Чехова, 2, корп. И, комн. 347.

С диссертацией можно ознакомиться в библиотеке ТРТУ.

Автореферат разослан " 5 " августа 2004 г.

Просим Вас прислать отзыв, заверенный печатью учреждения по адресу: 347928, г. Таганрог, Ростовская область, ГСП-17А, пер. Некрасовский, 44, Таганрогский государственный радиотехнический университет Ученому секретарю диссертационного совета Д 212.259.05 Кухаренко А.П.

Ученый секретарь диссертационного совета кандидат технических наук, доцент

Syppe

А.П. Кухаренко

#### ОБІНАЯ ХАРАКТЕРИСТИКА РАБОТЫ

Актуальность темы. Суперкомпьютеры предназначены для решения сложнейших проблем современности, требующих обработки гигантских объемов информации в короткие промежутки времени. Создание и использование суперкомпьютеров относится к факторам стратегического развития науки и техники и входит в первую десятку приоритетных технологий развитых стран. Без суперкомпьютеров невозможно моделировать экономические и социальные системы, прогнозировать экологические процессы и природные геофизические явления, разрабатывать важнейшие техногенные объекты, решать проблемы космонавтики, астрофизики, медицины. Развитие микроэлектроники и создание семейств высокопроизводительных микропроцессоров привело к тому, что доминирующим направлением построения суперкомпьютеров в настоящее время являются многопроцессорные вычислительные системы (МВС) с массовым параллелизмом, содержащие тысячи параллельно функционирующих микропроцессоров. О темпах развития вычислительной техники говорит тот факт, что два десятилетия назад наиболее мощные. суперкомпьютеры имели производительность в несколько Гфлопс; в настоящее время эксплуатируются суперкомпьютеры с производительностью более триллиона операций в секунду, наиболее мощные суперкомпьютеры имеют производительность, превышающую 50 Тфлопс, и разрабатываются системы с производительностью от 100 до 1000 Тфлопс.

В то же время при решении сложных научно-технических задач существующие МВС с массовым параллелизмом обеспечивают достаточно низкую реальную производительность, зачастую не превышающую 10-15 % от пиковой производительности системы, вследствие того, что организация параллельных вычислений и процедуры межпроцессорных обменов требуют больше времени, чем непосредственно вычисления. Это объясняется тем, что практически все существующие методы организации параллельных вычислений в МВС с массовым параллелизмом ориентированы на решение проблем адаптации структуры последовательного алгоритма к архитектуре МВС. До сих пор эти проблемы не решены, и это не позволяет создать масштабируемые параллельные программы для МВС с массовым параллелизмом, которые могли бы быть выполнены с одинаковой эффективностью на произвольной конфигурации вычислительной системы.

Как правило, при создании параллельных программ используются эвристические методы поиска локально-оптимальных вариантов построения множества взаимосвязанных последовательных процессов, и эффективные параллельные программы удается создать лишь для определенного варианта распараллеливания. В связи с этим программирование на МВС с массовым параллелизмом до сих пор является сложным и трудоемким процессом, намного превосходящим по сложности процесс программирования на однопроцессорных машинах. Это обуславливает чрезвычайно высокую стоимость прикладного и системного программного обеспечения МВС.

От эффективности математических методов и программно-аппаратных средств организации параллельных вычислений в значительной (пенсии зависит эффективность применения многопроцессорных систем для решения научно-технических задач.

the decembers 597

Поэтому актуальной является решаемая в диссертации научная проблема организации эффективных параллельных вычислений в многопроцессорных вычислительных системах с массовым параллелизмом, обеспечивающих их реальную производительность близкую к пиковой на широком классе задач. Решение этой проблемы обеспечит увеличение рентабельности высокопроизводительных вычислительных комплексов за счет более рационального использования оборудования многопроцессорных систем и сокращения времени, необходимого для организации параллельных вычислений, что, в свою очередь, позволит существенно сократить сроки и стоимость проведения фундаментальных исследований, а также решения важнейших прикладных задач народнохозяйственного значения и повышения обороноспособности страны.

Решением данной проблемы занимались такие видные ученые как Э. Дейкстра, Ч. Хоар, Р. Хокни, В. Хейдлер, Д. Чамберлсн, а также российские ученые: В.С. Бурцев, В.Е. Котов, В.К.Левин, Д.А. Поспелов, В.Г. Хорошевский, В.В.Воеводин, В.А. Вальковский и многие другие. Однако их исследования были ориентированы на разработку методов и аппаратно-программных средств параллельных вычислений для традиционной (жесткой) архитектуры МВС, что обеспечивает высокую реальную производительность только для некоторых классов задач.

Альтернативой существующим методам организации параллельных вычислений является организация вычислений для многопроцессорных систем с программируемой архитектурой, концепция которых была разработана академиком РАН А.В. Каляевым.

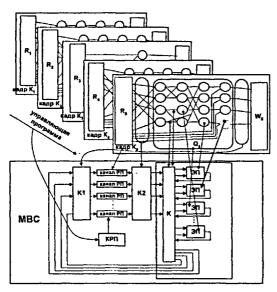

МВС с программируемой архитектурой (ПА) представляет собой множество элементарных процессоров (ЭП) и блоков (сегментов) распределенной памяти (РП), которые могут с помощью программно-аппаратных средств системы и пространственной коммутационной структуры объединяться в проблемно-ориентированные вычислители. Это позволяет не только подбирать структуру алгоритма к архитектуре системы, но и, наоборот, адаптировать структуру многопроцессорной системы к параллельному алгоритму. Для многопроцессорной системы с программируемой архитектурой используется структурно-процедурная организация параллельных вычислений, которая обеспечивает максимальную скорость обработки данных, сопоставимую со скоростью специализированных вычислителей. Однако реализация этих принципов требует разработки новых математических методов организации вычислительных процессов и создания аппаратно-программных средств для их поддержки.

<u>Целью работы</u> является разработка и создание формальных математических методов синтеза структурно-процедурных параллельных программ, эффективно реализуемых на различных конфигурациях многопроцессорных систем с программируемой архитектурой, и программно-аппаратных средств, обеспечивающих реальную производительность МВС ПА при решении задач различных классов, близкую к пиковой, а также линейный рост производительности при увеличении ресурсов системы.

В соответствии с поставленной целью определены задачи диссертации:

- 1) Провести анализ методов и моделей параллельных вычислений и на их основе разработать основные принципы эффективных структурно-процедурных вычислений.

- 2) Разработать формальные математические методы преобразования алгоритмов задач различных классов в структурно-процедурную форму, обеспечивающие решение за-

дач с реальной производительностью, близкой к пиковой производительности системы, для различных степеней распараллеливания.

- 3) Разработать средства описания структурно-процедурных вычислений на основе неявного представления параллелизма, обеспечивающие естественное и однозначное отображение параллельного алгоритма на архитектуру многопроцессорной вычислительной системы, а также эффективную реализацию масштабируемых параллельных программ.

- 4) Разработать технологию создания масштабируемых структурно-процедурных программ, обеспечивающую эффективную реализацию параллельных программ на различных конфигурациях МВС ПА, и рост производительности, близкий к линейному, при увеличении ресурса системы, выделенного для решения задачи.

- 5) Разработать аппаратно-программные средства, обеспечивающие реализацию структурно-процедурных вычислений на уровне элементной базы.

- Разработать аппаратные средства для эффективной реализации структурнопроцедурных вычислений на основе модульно-наращиваемых многопроцессорных систем.

Методы исследования. При решении поставленных задач использовались элементы теории вычислительных систем, элементы теории графов, теории множеств, а также реляционное исчисление. Теоретические исследования подтверждены вычислительными экспериментами на имитационной модели МВС со структурно-процедурной организацией вычислений, а также реализацией программных средств на созданных модульно-наращиваемых МВС ПА в интересах ряда предприятий и организаций.

Научная новизна диссертации заключается в том, что в ней впервые:

- 1)На основе формального определения структурно-процедурной организации вычислений разработаны методы приведения регулярных графов алгоритмов в структурно-процедурную форму, которые обеспечивают синтез семейства параллельных алгоритмов с различной степенью параллелизма и эффективностью реализации на МВС ПА, сравнимой с эффективностью специализированных вычислителей.

- 2) Разработаны методы приведения произвольного информационного графа алгоритма в функционально-регулярную форму и синтеза на его основе структурнопроцедурного алгоритма, позволяющие в несколько раз повысить эффективность реализации на МВС ПА параллельных программ решения функционально-нерегулярных задач по сравнению с традиционными методами организации параллельных вычислений.

- 3)Для структурно-процедурной организации вычислений разработан язык программирования высокого уровня, ориентированный на неявное представление параллелизма с помощью объявления типов массивов переменных и индексации их элементов и, как следствие, позволяющий получать различные варианты распараллеливания задачи при модернизации структуры данных.

- 4) В языке программирования высокого уровня предложено следующее ограничение правила единственной подстановки, широко используемой в языках потоков данных для представления неявного параллелизма: каждая переменная в программе получает значение один раз в теле описания вычислительной структуры кадра, что обеспечивает детерминизм реализации параллельной программы и позволяет достигнуть взаимноод-

позначного соответствия описания вычислительной структуры кадра информационному графу решения фрагмента задачи.

- Разработаны алгоритмы трансляции с языка программирования высокого уровня, учитывающие специфику организации параллельных вычислений и методы синтеза бесконфликтных процедур обращения к распределенной памяти.

- 6) Разработаны принципы построения технологии индуктивных структурнопроцедурных программ, представленных в виде графа минимальной конфигурации, и правил его наращивания при увеличении аппаратного ресурса системы.

- 7) Разработана система операций модификации кадровых структур при увеличении аппаратного ресурса, выделенного для решения задачи, и степени распараллеливания. Применение системы операций модификации кадровых структур обеспечивает близкий к линейному рост производительности при увеличении числа базовых модулей МВС, выделенных для решения задачи.

- 8) На основе анализа различных вариантов построения структуры распределенной памяти показано, что для многопроцессорных систем наиболее рациональной является архитектура распределяемой памяти.

- 9) Показано, что для структурно-процедурных вычислений возможно уже на этапе трансляции задачи, в силу детерминизма вычислительного процесса, определить множество коммутационных структур, которые необходимо последовательно реализовывать в пространственной коммутационной системе. Такое свойство позволит существенно уменьшить аппаратные затраты на построение коммутационной структуры.

<u>Достоверность и обоснованность</u> полученных в работе результатов подтверждается полнотой и корректностью исходных посылок, теоретическим обоснованием, непротиворечивостью математических выкладок. Теоретические исследования подтверждены вычислительными экспериментами на имитационной модели МВС ПА, а также реализацией компонентов математического обеспечения на базовом модуле МВС со структурнопроцедурной организацией вычислений (МВС со СПОВ).

<u>Научная и практическая ценность работы.</u> Практическое использование научных результатов позволило:

- 1) Повысить реальную производительность многопроцессорных систем при решении ряда задач различных проблемных областей. На основе разработанных в диссертации методов создан ряд параллельных алгоритмов и параллельных программ, повышающих эффективность распараллеливания в 2-5 раз по сравнению с известными решениями.

- 2) Разработать и создать язык программирования высокого уровня с неявным описанием параллелизма, позволяющий сократить время создания параллельных масштабируемых программ, эффективно реализуемых на различных конфигурациях многопроцессорной системы.

- 3) Разработать алгоритмы планировщика индуктивных заданий, распределяющего свободный ресурс системы с минимизацией времени прохождения потока заданий. Реализация планировщика заданий показывает его высокую эффективность, в том числе, и для ограниченных коммутирующих структур, для которых преимущество технологии индуктивных структурно-процедурных программ более заметно и позволяет повысить

коэффициент использования оборудования на 40% и сократить время прохождения задач на 20--30%.

- 4) Разработать алгоритмы системы посттрансляции, осуществляющие модернизацию загрузочного модуля параллельной программы на более высокой степени распараллеливания и перекоммутацию пространственных связей между базовыми модулями, выделенными планировщиком заданий (ПЗ) для решения задачи.

- 5) Разработать и создать элементную базу для построения MBC со СПОВ, с минимальной номенклатурой и четко обозначенными функциями. Технические решения защищены четырьмя патентами РФ.

- 6) Разработать и создать одноплатные базовые модули с иерархической коммутационной и ортогональной коммутационной системами, аппаратно-программные средства которых позволили обеспечить повышение реальной производительности по сравнению с традиционными архитектурами на порядок, а удельной производительности на два порядка. Набольший рост производительности достигается для наиболее сложных сильносвязанных задач, для которых, как правило, ранее не было известно эффективного параллельного решения.

- 7) Разработать и создать модульно-наращиваемые многопроцессорные системы со структурно-процедурной организацией вычислений, используемые для решения широкого класса задач в различных организация и ведомствах.

Предложенные в диссертации новые решения строго аргументированы и критически оценены по сравнению с другими известными результатами. В диссертации приведены рекомендации по использованию полученных научных выводов. Полученные научные результаты практически используются на различных предприятиях и в организациях РФ, что подтверждается соответствующими актами о реализации. В диссертации решена крупная научная проблема, которая является актуальной и имеет важное научнохозяйственное значение. Внедрение полученных в диссертации результатов вносит значительный вклад в развитие экономики страны и повышение ее обороноспособности.

Реализация и внедрение результатов работы. Теоретические и практические результаты диссертационной работы использованы при выполнении госбюджетных и хоздоговорных НИР в НИИ МВС ТРТУ, непосредственным участником которой являлся автор диссертации. Результаты диссертации внедрены в ОАО "Научно-исследовательский центр электронной вычислительной техники" (НИЦЭВТ), г. Москва; Московском государственном институте электронной техники (технический университет), г. Москва; в/ч 26165, г. Москва; в/ч 25714, г. Курск; Таганрогском государственном радиотехническом университете, г. Таганрог, НИИ многопроцессорных вычислительных систем Таганрогского государственного радиотехнического университета, г. Таганрог; Научно-конструкторском бюро вычислительных систем Таганрогского государственного радиотехнического университета, г. Таганрог.

Апробация работы. Основные результаты работы докладывались и обсуждались на всероссийских и международных научно-технических конференциях: International Conference "Parallel Computing Technologies (PaCT)", Novosybirsk, 1991; Yaroslavl, 1997; Всероссийская научно-техническая конференция с международным участием "Теория цепей и сигналов", Новочеркасск, 1996; VI международный семинар "Распределенная

обработка информации", Новосибирск, 1998; IV, V Всероссийские научно-технические конференции ""Нейрокомпьютеры и их применение", Москва, 1998 - 1999; Международные конференции "Интеллектуальные многопроцессорные системы (ИМС'99)", Таганрог, 1999, пос. Дивноморское, 2001,2003; Международная конференция "Искусственный интеллект",-Кацивели, 2000, 2002; Международная научно-техническая конференция "СуперЭВМ и многопроцессорные вычислительные системы", Таганрог, 2002; Всероссийская научная конференция "Высокопроизводительные вычисления и их приложения", Черноголовка, 2000; Третья международная научно-техническая конференция "Электроника и информатика - XXI век", Зеленоград-Москва, МИЭТ, 2000; Между народная конференция "Параллельные вычисления и задачи управления (РАСО'2001)", М: ИПУ РАН им. В.А.Трапезникова, 2001; Конференция "С.А. Лебедев и развитие отечественной вычислительной техники", Москва, ИПИ РАН, 2002; Всероссийская научная конференция "Методы и средства обработки информации", Москва, ф-т вычислительной математики и кибернетики МГУ им. М.В. Ломоносова, 2003.

#### Основные положения, выносимые на защиту:

- 1)Доказательство более высокой эффективности (отношение ускорения, достигаемого на МВС по сравнению с однопроцессорной ЭВМ, к числу процессоров) структурно-процедурных вычислений по сравнению с традиционными методами организации параллельных вычислений.

- 2) Принципы и методы преобразования алгоритмов в структурно-процедурную форму, эффективно реализуемую в МВС ПА для различных степеней распараллеливания, обеспечивающие линейный рост производительности при увеличении ресурсов системы.

- 3) Язык программирования высокого уровня для описания структурнопроцедурных вычислений на основе неявного представления параллелизма за счет объявления типов массивов переменных и индексации их элементов, обеспечивающий естественное и взаимодополняющее отображение параллельного алгоритма в структуру многопроцессорной вычислительной системы.

- 4) Технология индуктивных программ, обеспечивающая высокую эффективность решения структурно-процедурных программ на различных аппаратных ресурсах и сокращение времени прохождения потока заданий.

- 5) Программно-аппаратные средства поддержки структурно-процедурных вычислений на уровне элементной базы, позволяющие достигать реальной производительности системы, близкой к пиковой, для широкого класса задач и повышающие удельную производительность системы.

- 6) Аппаратные средства, обеспечивающие реализацию структурно-процедурных вычислений на основе модульно-наращиваемых многопроцессорных систем для различных вариантов распараллеливания задачи различных проблемных областей.

<u>Личный вклад автора.</u> Все научные результаты, полученные при решении крупной научной проблемы создания методов структурно-процедурного программирования и программно-аппаратных средств, обеспечивающих реальную производительность МВС при решении задач различных классов, близкую к пиковой, а также линейный рост производительности при увеличении ресурсов системы, получены автором лично.

<u>Публикации.</u> По теме диссертации опубликованы 102 печатные работы, в том числе, 1 монография, 30 статей в центральной печати, из них 10 - в изданиях, входящих в "Перечень ведущих научных журналов и изданий, выпускаемых в Российской Федерации" ВАК, получено 4 патента на изобретение.

<u>Структура и объем диссертации</u>. Диссертация состоит из введения, шести разделов, заключения и списка литературы из 232 наименований. Она содержит 363 страницы текста, 11 таблиц, 156 рисунков, 62 страницы приложений.

#### КРАТКОЕ СОДЕРЖАНИЕ РАБОТЫ

**Во введении** обосновывается актуальность проблемы, проанализирован научный уровень методов организации параллельных вычислений, сформулированы цель и задачи исследования, дан краткий обзор содержания диссертации, перечислены полученные научные результаты и приведены сведения о практической ценности работы.

<u>В первой главе</u> проведен аналитический обзор методов организации параллельных вычислений. Показаны нерешенные проблемы в области создания параллельных алгоритмов. Разработаны основные принципы преобразования задач различных классов в структурно-процедурную форму.

Большинство существующих MBC использует мультипроцедурную организацию вычислений, когда в каждом процессоре реализуется последовательная программа, а для обмена данными между процессорами в системе организуются специальные процедуры. Существующие системы распараллеливания для таких MBC ориентированы на решение определенного класса задач или вносят большие накладные расходы, в результате параллельные программы решения сложных задач имеют низкую реальную производительность.

В последнее время появились реконфигурируемые системы, позволяющие синтезировать вычислительные структуры, адекватные решаемой задачи. Однако такие системы перестраиваются с одной структуры на другую за очень большое время, что ограничивает их применение для различных классов задач, таких как система HC Starbridge, или применяются только для систолических вычислений и сводимых к ним задач, например, система Хриter.

Альтернативой существующим MBC с массовым параллелизмом являются многопроцессорные вычислительные системы с программируемой архитектурой, концепция которых разработана в Научно-исследовательском институте многопроцессорных систем ТРТУ под руководством академика РАН А.В. Каляева. МВС с программируемой архитектурой обеспечивает пользователю возможность формировать в универсальной системе виртуальные специализированные вычислители, адекватные структуре решаемой задачи, что выводит на передний план "внутренний" параллелизм задачи. В тоже время формальные методы синтеза структурно-процедурных решений для задач различных классов не созданы.

Для более детального анализа целесообразно рассмотреть общую структуру задачи - информационный граф алгоритма. В информационном графе вершины соответствуют

исходным данным, операциям над данными и результатам вычислений. Дуги информационного графа соответствуют информационным связям алгоритма.

Если множество вершин V информационного графа G может быть представлено в виде объединения некоторых непересекающихся подмножеств

$$V = \bigcup_{i=1}^{k} V_i \tag{1}$$

таких, что если вершина  $\boldsymbol{u} \in \boldsymbol{V_i}$ , а вершина  $\boldsymbol{v} \in \boldsymbol{V_j}$ ,  $\boldsymbol{i} < \boldsymbol{j}$ , и существует дуга  $\langle \boldsymbol{u}, \boldsymbol{v} \rangle$ , то такое разбиение называется параллельной формой алгоритма. При описании задачи информационным графом все ее циклические участки итерированы столько раз, сколько должен повторяться этот участок. Если количество итераций неизвестно, то можно представить некоторую итерированную структуру с неизвестным числом повторений. При этом предполагается, что операции алгоритма разбиты на группы, упорядоченные так, что каждая операция любой группы зависит либо от начальных данных алгоритма, либо от результатов выполнения операций, находящихся в предыдущих группах.

Для мультипроцедурных методов организации параллельных вычислений широкое распространение получили ярусно-параллельные формы (ЯПФ). Представление графа алгоритма в ярусно-параллельной форме заключается в упорядочении вершин графа по подграфам  $V_i$  разбиения (1). Упорядоченные подмножества называются ярусами. Множество нулевого яруса  $V_0$  определяет совокупность входных вершин X. В общем случае, вершина d принадлежит i-му ярусу тогда и только тогда, когда существует, по крайней мере, хотя бы одна дуга  $A = \langle c, d \rangle$ , где c — вершина, принадлежащая ярусу с номером i-I. Данное утверждение можно записать в реляционном исчислении следующим образом:

$$V_i = \{c \mid A(\langle c, d \rangle) \land V_{i-1}(d)\}. \tag{2}$$

При соблюдении только условия (2) формируется ярусно-конвейерный граф, в котором разрешены обратные связи. Достоинством параллельно-конвейерной формы представления задач является ее большая компактность по сравнению с ярусно-параллельной формой. Однако если необходимо перейти к другому варианту распараллеливания задачи, требуется разрывать рекурсивные связи, что представляет сложную проблему при реализации эффективных параллельных программ.

Поэтому для преобразования задачи в параллельную форму, эффективно реализуемую для различных вариантов распараллеливания, необходимо использовать альтернативные способы представления параллельного алгоритма. В общем, информационный граф можно представить в виде:

$$G = \langle (X, \Lambda_X), (Q, \Lambda_Q), (Y, \Lambda_Y) \rangle, \tag{3}$$

где Х- множество входных вершин графа,

У- множество выходных вершин,

Q - множество операционных вершин.

Объединение множеств входных дуг  $A_X$ , операционных дуг  $A_Q$  и выходных дуг  $A_Y$  описывает информационные связи в задаче. Для любой дуги (u,v), принадлежащей к  $A_X$ , вершина  $u \in X$ , а вершина  $v \in Q$ . Для любой дуги (u,v) и надлежащей к  $A_{Q}$ , р ш и на  $u \in Q$  и вершина  $v \in Q$ . Для любой дуги (u,v) и надлежащей к  $A_{Q}$  р ш и на  $v \in Q$ .

Если число элементарных процессоров в системе не меньше числа операционных вершин, и все дуги информационного графа задачи (в том числе, обуславливающие связь между информационными и операционными вершинами) можно реализовать в пространственной коммутационной системе, то информационный граф задачи тривиальным образом реализуется в многопроцессорной системе. Операционная вершина графа будет соответствовать процессору, настроенному на выполнение определенной арифметикологической операции. Входная (выходная) информационная вершина должна соответствовать сегменту операционной памяти, в которой расположены исходные данные (результаты вычислений). Такую организацию вычислений будем называть структурной организацией вычислений. На практике обеспечить структурную организацию вычислений не представляется возможным, так как для се реализации требуется чрезвычайно большое количество процессоров. В этой связи возникает проблема, решаемая в диссертации, заключающаяся в сегментации информационного графа на пересекающиеся подграфы, которые структурно реализуются в системе, при этом обеспечивается минимальное время решения задачи.

Задача, описываемая в виде информационного графа G, может быть представлена в виде множества крупных функционально законченных вычислительных фрагментов  $P_i$ :

$$G = \bigcup_{i=1}^{M} P_i, \tag{4}$$

таких, что если вершина  $\boldsymbol{a} \in \boldsymbol{P_i}$  и вершина  $\boldsymbol{b} \in \boldsymbol{P_j}$  и существует хотя бы одна дуга ( $\boldsymbol{a}$ ,  $\boldsymbol{b}$ ), то  $\boldsymbol{i} \leq \boldsymbol{j}$ . Будем называть дуги, соединяющие подграфы, - внешними, а дуги, принадлежащие подграфу  $\boldsymbol{P_i}$ , - внутренними. Данное разбиение коренным образом отличается от ранее рассмотренных разбиений (1, 2) возможностью связей внутри фрагментов.

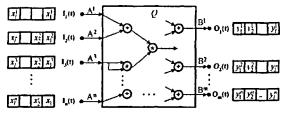

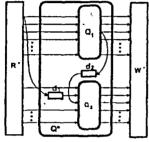

Подграфы информационного графа задачи, последовательно реализуемые на многопроцессорной системе, принято называть кадрами, а механизм последовательного обхода информационного графа задачи подграфами - структурно-процедурной программой. Кадр представляет собой структурно-реализованный подграф задачи, через который следует поток данных. Подобная организация вычислений обеспечивает максимальную скорость обработки данных, сопоставимую со скоростью специализированных вычислителей. Вычисления выполняются по принципу управления потоком данных и не требуют синхронизации. Настройка на кадры производится по единой управляющей программе, что обеспечивает фон-неймановский детерминизм. Кадр часто описывается как объект, определенный в виде тройки  $\langle Q,I,O \rangle$ , где Q - функциональный граф кадра; I, О - множество информационных потоков. На практике зачастую понимается, что информационные потоки, входящие в кадр, однозначно определены и соответствуют появлению входных данных в заданном временном масштабе. Однако, как показали проведенные исследования, такой взгляд на информационные потоки кадра является частным случаем. На рис.1, представлено графическое изображение кадра. Несложно заметить, что вышеприведенное определение кадра соответствует кортежу элементарных кадров  $(K_1, K_2, ..., K_l)$ , где l - размер информационных потоков на входе (выходе) кадра.

Элементарным кадром будем называть кадр, в котором на каждый вход функционального графа кадра подается только один операнд и с каждого выхода снимается толь-

Рис 1. Графическое изображение кадра.

ко один результат. Элементарный кадр определяется тройкой  $\langle Q, X_i, Y_i \rangle$ , где  $X_i$  и  $Y_i$  - это множества входных и выходных вершин, соответствующие информационному потоку в определенный момент времени. Множества входных и выходных вершин элементарного кад-

ра  $K_i$  можно определить следующим образом:  $X_i = I(t_i)$ ,  $Y_i = O(t_i)$ . Следует отметить, что функциональный граф всех элементарных кадров кортежа - изоморфный. На рис.2 представлено графическое изображение кортежа изоморфных кадров. Доказано, что если имеется кортеж элементарных кадров, каждый элемент которого обладает изоморфным функциональным графом, то такой кортеж можно представить в виде исполняемого кадра.

Рис.2. Кортеж изоморфных кадров.

Обращаясь к кортежам по индексу, можно получить требуемый элемент и, следовательно, информационные потоки можно определить как функции обращения к информационным массивам. Такой подход позволяет значительно расширить применение структурных и структурно-процедурных методов организации параллельных вычислений для задач различных проблемных областей и увеличить эффективность распараллеливания, а, как следствие, и сушественно сократить время и стоимость решения задачи на МВС. В общем случае, информационные потоки, поступающие на входы кадровых структур, определяются не временными соотношениями задачи, а информационными зависимостями алгоритма, в которых временные зависимости являются только частными случаями.

Под информационной зависимостью двух под графов  $G_l$  и  $G_2$  графа задачи понимается наличие пу-

ти в информационном графе задачи, соединяющем вершину  $a \in G_1$  и вершину  $b \in G_2$ . Следовательно, два подграфа будут информационно независимыми, если в информационном графе задачи не существует ни одного пути, соединяющего любые вершины, принадлежащие  $G_1$  и  $G_2$  Множество информационно-независимых изоморфных подграфов представлено в виде кадра. Доказано, что правило упорядочивания элементарных кадров в кортеж однозначно определяет порядок появления входных и выходных информационных вершин. Дополнительным условием, при котором кортеж подграфов может быть представлен в виде кадра, является наличие рекуррентных правил отображения входных и выходных дуг подграфов  $g_1$  (i=1,2,...,l-1):  $F_R:A_{X_1} \to A_{X_{1,1}}$  и  $F_W:A_{Y_1} \to A_{Y_{1,1}}$ .

Изоморфные графы, которые преобразуются в кадр, должны быть реализуемыми, т.е. к моменту инициализации кадра все информационные элементы, соответствующие входным вершинам всех информационных графов, должны быть получены и будут находиться в каналах распределенной памяти.

Полученные выражения расширены на наиболее общий случай, когда объединяются информационно зависимые подграфы, но дуги зависимости соединяют непосредственно информационные подграфы без дополнительных операционных вершин.

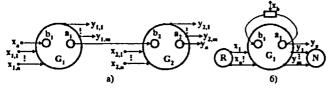

Если существуют два изоморфных подграфа  $G_I$  и  $G_2$ , не являющиеся информационно независимыми, и существует единственная дуга, начальная вершина которой является  $a_1 \in G_1$ , а конечной вершиной я в л я  $eb_T \in G_2$  и не существует другого пути информационной зависимости между подграфами  $G_I$  и  $G_2$ , то п о д г р  $a_1 \in G_2$  ж н о упорядочить в кадр, при этом имеется единственное правило упорядочивания  $a_1 \in G_1$ ,  $a_2 \in G_2$ , определенное дугой  $a_1 \in G_2$ . В этом случае производится дополнительное преобразование информационного графа. Формируется дуга, соединяющая вершину  $a_1 \in G_1$  и вершину  $a_2 \in G_2$  изоморфны). На эту дугу вводится начальный элемент, обеспечивающий реализацию обратной связи. Начальное значение определяется начальной вершиной дуги, входящей в граф  $a_2 \in G_1$ . Вершина  $a_2 \in G_2$  изоморфны). Дуги  $a_2 \in G_1$  и  $a_3 \in G_2$  удаляются из графа кадра. Пример преобразования представлен на рис. 3, где а) исход-

ный подграф задачи; б) граф кадра.

Рис. 3. Преобразование связанных информационных графов в кадр.

Данные преобразования расширены на произвольное количество подграфов. Если имеется множество изоморфных подграфов  $G_1, G_2, ... G_8$ , являю-

щихся информационно-зависимыми только по смежным дугам  $\alpha_i$ , соединяющим подграфы  $G_i$  и  $G_{i+1}$  (начальной вершиной дуг смежности является  $a_i \in G_i$ , конечной вершиной -  $b_i \in G_{i+1}$  и вершина  $a_1$  является соединенной с входной вершиной  $X_{ij}$ , то под графы  $G_1, G_2, ... G_n$  могут быть преобразованы в кадр, причем, правило упорядочивания подграфов определяется путем, связующим подграфы  $\langle G_1, G_2, ... G_n \rangle$ . Пример такого графа показан на рис.4.

Рис.4. Информационный граф, содержащий изоморфные взаимосвязанные подграфы.

При объединении графа дуга  $\alpha_i$  исключается и формируется обратная связь  $\langle a,b \rangle$ , инициализируемая начальной вершиной, смежной по дуге  $\alpha_i$  с  $b_i$ , т.е.  $x_a$ . Структура графа кадра будет такая же, как на рисунке 36).

Показано, что информационных дуг, соединяющих подграфы, может быть множество (связи могут следовать не только через смежные фрагменты), но все они должны

быть описаны функциональной зависимостью между подграфами. Количество инициализаций (начальных значений по обратным связям) определяется разностью индексов между индексом начальной вершины  $a_i \in G_i$  и конечной в е р ш  $b_{i_1}$   $b_{i_2}$  В более общем случае выделяется функциональная зависимость между начальной вершиной  $a_i \in G_i$  и конечной вершиной  $b_{f(i)} \in G_{f(i)}$ . Следует отметить, что связь может быть не только между одиночными подграфами, но и некоторой совокупностью подграфов (слоев) между собой.

Очевидно, что связь между последовательно реализуемыми кадрами осуществляется только через оперативную память, которая для MBC со структурно-процедурной организацией вычислений является распределенной и многоканальной. Каждой входной дуге  $a_j$  кадра ставится в соответствие функция чтения  $r_j$ , отображающая моменты времени (такты работы системы) на множество операндов, т.е. обеспечивающая поступление информационных потоков на входы кадра из каналов распределенной памяти. Аналогично, каждой выходной дуге  $b_j$  кадра ставится в соответствие функция записи  $w_j$ , отображающая моменты времени (такты работы системы) на множество результатов, т.е. обеспечивающая сохранение информационных потоков с выходов кадра в каналах распределенной памяти.

Будем называть информационным кадром следующую тройку: K = < R, Q, W >, где R - узел чтения; Q- структурно-реализованный подграф задачи; W- узел записи. Здесь

$$R = \bigcup_{j=1}^{N(A)} \langle a_j, r_j \rangle, \tag{5}$$

где N(A) - мощность множества входных дуг кадра A.

Аналогично узел записи представляет собой объединение упорядоченных пар:

$$W = \bigcup_{j=1}^{N(B)} \langle b_j, w_j \rangle, \tag{6}$$

где  $N(B_i)$  - мощность множества выходных дуг кадра.

В диссертации определены дополнительные условия разбиения информационного графа задачи на структурно-реализуемые подграфы. Каждый фрагмент должен быть представлен в виде множества подграфов

$$P_i = \bigcup_{i=1}^N S_{i,j} \tag{7}$$

таких, что если существует хотя бы одна дуга (a,b) и вершина  $a \in S_{ki}$ , а вершина  $b \in S_{kj}$ , то  $i \le j$ . Подграфы  $S_{ij}$  будем называть слоями. При этом дуги, соединяющие слои, будем называть межслойными дугами, а дуги, соединяющие операционные вершины одного слоя, будут внутрислойными дугами. Наконец, каждый подграф  $S_{i,j}$  можно представить в виде множества подграфов

$$S_{i,j} = \bigcup_{k=1}^{K} g_{i,j,k}, \qquad (8)$$

при этом все подграфы  $g_{ij,k}$  должны быть изоморфны друг другу. Подграфы  $g_{ij,k}$  будем называть базовыми подграфами.

Кроме того, выполняются следующие условия. Внутрислойные дуги должны прина-

длежать какому-нибудь базовому подграфу. Если существует дуга  $(a,b) \in S_{i,j}$ , то вершина  $a \in g_{i,j,k}$  и вершина  $b \in g_{i,j,k}$ . Как следствие, не существует дуг, соединяющих вершины, принадлежащие базовым подграфам одного слоя. Базовый подграф  $g_{i,j,k} \notin \mathfrak{S}_{i,j}$  и только тогда, когда существует, по крайней мере, одна дуга (a,b) такая, что  $a \in q_{ij-lj}$  и  $b \in q_{ijk}$ .

Подобное представление графа в виде множества подграфов будем называть секвенцией графа. Секвентированный граф вычислительного процесса решения задачи может быть представлен в виде

$$P_{i} = \Phi_{i,l}(F_{i,l,k}(g_{i,l,k})), \tag{9}$$

где  $F_{i,j,k}$  — функция, отображающая дуги базового подграфа  $g_{i,j,k}$  на базовый подграф  $g_{i,j,k+1}$ ,  $\phi_{i,j}$  — функция, отображающая множество дуг слоя  $S_{i,j}$  на множество дуг слоя  $S_{i,j+1}$ . Множество функций F является описанием параллельного выполнения базовых подграфов. Множество функций  $\phi$  определяет информационную зависимость между слоями.

Если в результате выполнения секвенции в подграфе  $P_m$  подграфы  $g_{l,n,k} \in S_{l,n}$  и  $g_{l,m,k} \in S_{l,m}$  изоморфны для всех значений k, n и m и существуют обобщающие функции отображения базовых подграфов внутри слоя и функции отображения слоев друг на друга, то такое разбиение графа вычислительного процесса решения задачи G на подграфы  $P_l$  будем называть функциональным секвентированием.

При функциональном секвентировании фрагменты  $P_i$  являются функциональнорегулярными  $P_i = \Phi_i(F_i(g_i))$ . Информационный граф алгоритма задачи, представленный в этом виде, будет называться функционально-регулярной формой графа вычислительною процесса решения задачи.

Показано, что кажущееся ограничение на возможность представления произвольного графа в функционально-регулярной форме не соответствует действительности. Любой граф вычислительного процесса может быть представлен, по крайней мере, в тривиальной функционально-регулярной форме, когда фрагмент графа содержит единственный слой, а слой содержит единственный базовый подграф. Тогда фрагмент представляется в виде элементарного кадра. Для увеличения эффективности параллельных программ целесообразно осуществлять секвенцию информационного графа в функционально-регулярную форму так, чтобы мощности множества слоев фрагмента и множества базовых подграфов слоя были как можно большими.

При формировании кадра происходит объединение множеств входных (выходных) информационных вершин в функциональный узел чтения (записи), дугам которого поставлен в соответствие кортеж функций. Элемент кортежа функций чтения ставит в соответствие моменту времени t множество (группу) входных информационных вершин x. Формируется операционная структура кадра, которая описывается графом  $Q=(V_O, A_b)$ .

Показано, что для эффективной реализации параллельных вычислений целесообразно, чтобы память MBC состояла из множества сегментов (каналов), при эти данные, требующие параллельного обращения, должны быть расположены в разных сегментах памяти. В результате массивы данных являются двумерными, при этом первое измерение определяет номер сегмента (канала), а второе — адрес в ячейке канала. Важной проблемой является синтез единой для всех кадров задачи структуры данных. Чтобы реализовать бесконфликтное параллельное обращение к каналам памяти многопроцессорной

системы, сформулирована система ограничений, позволяющих выбрать ограниченное количество вариантов размещения данных в сегментированной памяти в соответствии с выбранным вариантом распараллеливания задачи и конфигурацией МВС.

Система ограничений включает в себя фундаментальные ограничения, невыполнение которых не позволяет реализовать выбранный вариант распараллеливания в архитектуре вычислительной системы, а также дополнительные ограничения, невыполнение которых лишь уменьшает эффективность реализации задачи.

Фундаментальное ограничение параллельного доступа требует, что если функция чтения (записи) ставит в соответствие моменту времени t два операнда, то они должны быть расположены в разных каналах распределенной памяти. Кроме того, существует фундаментальное ограничение на количества каналов РП и элементарных процессоров.

Одной из основных задач организации эффективных структурно-процедурных вычислений является уменьшение времени решения задачи, что достигается минимизацией числа кадров и максимизацией размеров потока данных, обрабатываемых в кадрах, и минимизацией времени поступления операнда. Дополнительное ограничение регулярности накладывается на размещение элементов в сегментированной памяти многопроцессорной системы таким образом, чтобы программные затраты на реализацию функций чтения и записи были минимизированы.

В соответствии с системой фундаментальных ограничений выбирается рациональный вариант размещения элементов многомерных массивов в распределенной памяти МВС. На основании функций чтения и сформированной структуры данных реализуются рекуррентные выражения для функции адресации и коммутации в каждом кадре.

При работе с двумерными массивами индексы обоих переменных, в общем случае, зависят друг от друга В то же время для каждого канала распределенной памяти необходимо выполнить фиксированную процедуру обращения к данным, расположенным в канале, независимо от коммутации, для чего следует преобразовать функции адресации так, чтобы они зависели только от номера канала и момента времени обращения к данным. Для организации независимых процедур доступа к ячейкам РП (ar, aw) в канале в диссертации предложено осуществить переход от кортежей функций адресации и коммутации к кортежу функций исполнительной адресации чтения  $FE_R$  и кортежу функций исполнительной адресации чтения  $FE_R$  определяется следующим образом:

$$er_c = \bigvee_{k=0}^{r} (Dr_{k,c}) \cdot t_k = \bigvee_{k=0}^{r} A_c (x_{k,\alpha(k,c)}^J) \cdot t_k = ar_{\alpha(k,c)},$$

(10)

где  $Dr_{k,c}$  - адрес чтения в канале РП с логическим номером c в момент времени  $t_k$ ;

$\alpha(k,c)$  - номер элемента вектора коммутации чтения, значение которого в момент времени  $t_k$  равно c.

Аналогично,  $\pmb{c}$ -й элемент  $\pmb{ew_C}$  кортежа функций исполнительной адресации записи  $\pmb{FE_W}$  определяется следующим образом:

$$ew_c = \bigvee_{k=0}^{r} (Dw_{k,c}) \cdot t_k = aw_{\beta(k,c)} \cdot t_k, \tag{11}$$

где  $Dw_{kc}$  - адрес записи в канале РП, имеющем логический номер c в момент времени  $t_{ki}$

$m{eta}(k,c)$  - номер элемента кортежа функций коммутации записи, значение которого в момент времени  $t_k$  равно c.

После преобразования информационных подграфов в кадровую форму задача представляется в виде графа кадров, в котором каждой вершине ставится в соответствие кадр. Если между фрагментами задачи  $P_k$  и  $P_m$  существует информационная зависимость, описываемая множеством дуг  $D_{k,m}$ , то при преобразовании графа задачи в граф кадров множество дуг  $D_{k,m}$  заменяется дугой информационной зависимости  $(K_k, K_m)$ . Граф кадров может быть, в свою очередь, представлен в параллельной форме.

Структурно-процедурная организация вычислений накладывает на реализацию графа кадра следующее ограничение: в МВС одновременно может быть реализован только один кадр, что обеспечивает фон-неймановский детерминизм программы. При такой организации вычислительного процесса легко преобразовать граф кадров в структурно-процедурную форму. В самом деле, кадр можно рассматривать как некоторый функциональный оператор. Тогда можно выделить повторяемые (итерируемые) участки вычислений и реализовать их в виде циклов.

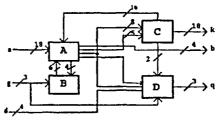

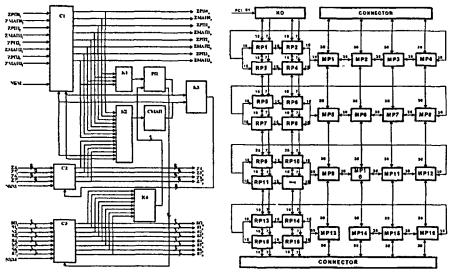

Рис.5. Отображение кадровой структуры на архитектуру MBC ПА.

Появляются альтернативные ветки алгоритма и т.д. В целом процесс преобразования задачи из графа кадра В структурнопроцедурную программу соответствует синтезу последовательной программы для однопроцессорной ЭВМ, и здесь можно воспользоваться всем опытом подобного синтеза. Компоненты кадров задачи естественным образом отображаются в структуру МВС ПА (рис.5). Так, внутренние (операционные) дуги базового подграфа отображаются на множество коммутационных связей, реализуемых в коммутаторе К, множество операционных вершин базового фрагмента - во множество элементарных процессоров. Множес тво входных и выходных луг базо-

вого фрагмента реализуется во множестве коммутационных связей коммутаторов  $K_1$  и  $K_2$ .

Массивы данных отображаются на множество адресов распределенной памяти.

Управляющая программа смены кадров и процедуры обращения к каналам распределенной памяти осуществляется в контроллере распределенной памяти (КРП).

<u>Во второй главе</u> на основании принципов организации структурно-процедурных вычислений разрабатываются методы преобразования алгоритмов решения задачи в

структурно-процедурную форму. Показано, что функционально-регулярный граф может быть реализован в виде единственного кадра, который представляет собой структурно-реализованный базовый подграф или множество взаимосвязанных базовых подграфов, через который следует поток данных. При этом элемент потока данных соответствует множеству информационных вершин на входах структурно-реализуемого подграфа.

При объединении базовых подграфов в кадр формирование обратных связей происходит не во всех случаях, а только когда ресурса системы достаточно для структурной реализации множества подграфов и время следования операндов одного слоя через структуру меньше времени заполнения конвейера. Определены условия формирования рекурсивных связей и время выполнения кадра.

Время выполнения кадра можно определить по следующей формуле:

$$T_k = t_1(Q) + t_n + \tau \cdot N, \qquad (12)$$

где  $t_3(Q)$  - время заполнения конвейера графа кадра;

${\it t_{H}}$  - время настройки на кадр;

N - размер потока данных, следующих через кадр;

**7** - время следования операнда.

Время следования операнда можно оценить по формуле:

$$\tau = \max(t_l(Q), t_0),\tag{13}$$

где  $t_0$  - время следования операнда в потоке;  $t_1$  - максимальная величина задержки по обратной связи в графе Q.

При большой величине N временем заполнения конвейера и временем настройки на кадр можно пренебречь. Время вычисления кадра можно оценить как

$$T_{k} \approx t_{0} \cdot N . \tag{14}$$

Однако если существует рекурсивная связь, то время выполнения кадра замедляется до величины

$$T_k \approx t_l(Q) \cdot N. \tag{15}$$

При достаточно больших структурных фрагментах это время может многократно превысить минимальное время выполнения кадра. Величину  $t_l(Q)$  можно оценить как  $m \cdot t_0$ , где  $m \sim \sqrt{M}$ , здесь M - число вершин в графе кадра.

Когда слой фрагмента информационного графа, преобразуемого в кадр, содержит n базовых подграфов, требование рекурсивной связи можно записать как выполнение условия

$$t_0 \ge \frac{T_p}{|p/p|},\tag{16}$$

где p - число одновременно реализуемых базовых подграфов.

Поэтому целесообразно повысить степень распараллеливания p только до тех пор, пока справедливо неравенство (16). В противном случае время решения задачи существенно увеличится. В диссертации на примере задачи математической физики показано применение методов структурно-процедурной организации вычислительного процесса для функционально-регулярных задач.

Выделено несколько основных типов информационных графов процесса решения задачи, для отображения которых в структурно-процедурную форму требуется выполнение специальных информационно-эквивалентных преобразований. К таким графам сле-

дуст отнести информационные графы (подграфы) решения задачи, которые хоть и имеют детерминированную структуру и могут быть представлены в виде кортежа информационно-зависимых подграфов (слоев), но функциональная зависимость между базовыми подграфами явно не выражена. Второй тип графа представляют собой задачи, у которых количество базовых подграфов, принадлежащих слою, одинаково, но правила отображения базовых подграфов внутри каждого слоя различны, а правило отображения слоев определяется конкретной реализацией данной задачи. Кроме того, существуют задачи, графы вычислительного процесса решения которых содержат различное и заранее неизвестное количество базовых подграфов, принадлежащих слою. При этом мощность слоя, содержащего базовые подграфы, зависит от результатов вычислений на предыдущих слоях графа (подграфа) задачи.

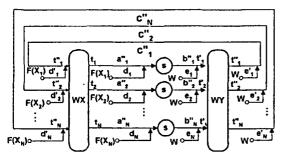

Для нерегулярных задач предложен комплекс преобразований. На первом этапе алгоритм задачи представляется в параллельной форме - в виде графа вычислительного процесса решения задачи. На втором этапе устраняется функциональная избыточность графа и формируется промежуточный функционально-нерегулярный граф. На третьем этапе выполняется специальное преобразование - векторизация информационных вершин, при выполнении которого множество непересекающихся подмножеств информашионных вершин, в каждом из которых существует ациклический путь, соединяющий в определенном порядке информационные вершины, или другое правило детерминированного упорядочивания вершин, заменяется специальным объектом — вершиноймассивом. Ланная вершина соответствует расположению структуры данных в каналах распределенной памяти МВС. Каждое подмножество информационных вершин, соединенных ациклическим путем в информационном графе или отобранное другим правилом упорядочивания, будет расположено в отдельном канале распределенной памяти. Адреса, по которым будут расположены вершины в канале, взаимно однозначно соответствуют номеру вершины на пути, соединяющему эти вершины в графе, или номеру в кортеже упорядочивания. После выполнения операции векторизации информационные дуги, источниками или приемниками которых являлись векторизированные информационные вершины, исключаются и заменяются дугами, источником или приемником которых является вершина-массив. В векторизированном графе появляются адресные дуги, которые формируются по следующему правилу: началом адресной дуги является информационная адресная вершина с уникальным именем, соответствующим адресу информационной вершины, а концом - метка информационной дуги, выходящей (входящей) из вершины массива. Адрес соответствует номеру канала распределенной памяти, т.е. номеру упорядоченного в кортеж подмножества информационных вершин. Каждая адресная дуга имеет признак t, который соответствует временной метке обращения по адресу ячейки в канале распределенной памяти. На рис.6 представлен граф процедуры построения гистограммы, которая широко используется при решении многих залач обработки сигналов и изображений. После преобразования информационного избыточного графа операция над данными производится по адресу элемента массива гистограмм.

Адресом служит функция F(x), которая определяет: к какому элементу гистограммы относится пришедший операнд  $x_i$ . Полученные результаты записываются в промежуточную вершину-массив WX.

Рис. 6. Пример *W*-графа, после выполнения векторизации информационных вершин.

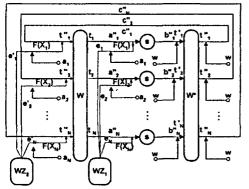

Однако при решении ряда задач, например, задачи трассировки, применения однократной векторизации информационных вершин недостаточно, поэтому необходимо использовать процедуру вторичной векторизации.

Поэтому в отличие от первичной векторизации здесь предложено в вершину-массив преобразовывать адресные признаки

F(x) и F(y), которые можно рассматривать как информационные адресные вершины.

В результате вторичной векторизации адресных вершин (рис. 7) формируется функционально-регулярный граф, в котором правила отображения дуг подграфов определены через правила отображения адресных вершин.

Рис.7. Вторичная векторизация адресных вершин.

Существуют задачи, информационные графы которых не структурированы и определяются некоторым внешним описанием. Эффективно реализовать в структурно-процедурной форме задачи подобного рода ранее описанными методами не представляется возможным. К числу таких задач относятся задачи логического и функционального моделирования. Несмотря на то что имеется определенный цикл повторения крупных участков задачи, соответствующих состоянию моделируемой схемы в определенный момент

времени, взаимосвязь между элементами для каждой моделируемой схемы различна. Разработан алгоритм мажорирования таких графов. В результате предложенного в диссертации преобразования формируется параллельный информационный граф. При этом связи между слоями параллельного информационного графа однозначно соответствуют коммутации между процессорными элементами (номерами, которыми отмечены операционные вершины). Данная коммутация должна меняться каждый такт.

С помощью разработанных методов возможно преобразовать в структурнопроцедурную форму даже нерегулярные информационные графы задач, таких как логическое моделирование, хотя МВС со структурно-процедурной организацией вычислений наиболее эффективны для сильносвязанных функционально-регулярных задач.

Как известно, распараллеливание еще не гарантирует увеличение производительности. Поэтому важным является вопрос о выборе оптимального варианта распараллеливания. В диссертации проведено сравнение эффективности структурно-процедурных и мультипроцедурных методов организации вычислительных процессов. Для простоты

рассуждения будем считать, что каждый слой содержит n базовых подграфов. Общее число слоев фрагмента равно m

Время решения задачи определятся суммой времен выполнения кадров:

$$T = \sum_{i=1}^{Z} T_{Ki} \,. \tag{17}$$

Время выполнения кадра существенным образом зависит от степени распараллеливания. Когда число процессоров, отведенных для решения задачи, не превышает K - число арифметико-логических операций в базовом подграфе, то время выполнения кадра на N процессорах определяется по следующей формуле:

$$T_{CH}(N) = mn \left[ \frac{K}{N} \right] (t_N + t_3(K) + \tau)$$

(18)

Если №Ж, то

$$T_{C\Pi}(N) = t_n + t_n(K) + \tau m \left[ \frac{n}{[N/K]} \right]$$

(19)

Эффективность распараллеливания  $E(N) = \frac{T(1)}{T(N) \cdot N}$  можно оценить

$$E(N) = \frac{m(t_n + t_2 + \tau \cdot n)}{t_n + t_2(K) + \tau \cdot m \cdot n}.$$

(20)

Эффективность структурно-процедурной организации вычислений существенно возрастает, как только число процессоров сравняется с числом арифметико-логических операций в базовом подграфе. В этом случае происходит скачок производительности, т.к. можно осуществлять конвейер не только по базовым подграфам одного слоя, но и по базовым подграфам всех слоев структурно-реализуемого фрагмента, и тогда эффективность превысит единицу, т.е. производительность системы вырастает в большее число раз, чем число процессоров.

Таким образом, если справедливо неравенство

$$m(t_H + t_3) > t_H + t_3(K),$$

(21)

то эффективность распараллеливания задачи будет больше единицы. Для МВС со структурно-процедурной организацией вычислений для большинства задач неравенство (21) справедливо. В частности, для задачи математической физики число узлов сетки существенно превышает число операций в узле сетки. Для задач цифровой обработки сигналов число отсчетов много больше, чем число операций по преобразованию сигналов. Для задач САПР число обрабатываемых элементов в тысячи раз больше, чем количество операций по преобразованию элементов.

Для MBC традиционных архитектур такая эффективность распараллеливания не достижима. Время выполнения задачи для мультипроцедурного метода распараллеливания

$$T_{m}(N) = \begin{cases} T_{m1}(N), \ ecnu \ N \le n, \\ T_{m2}(N), \ ecnu \ N > n. \end{cases}$$

3 десь  $T_{m1}(N) = m \cdot K(t_{n} + t_{3} + \tau) \frac{n}{N} \left[ \right], \quad T_{m2}(N) = \frac{m \cdot K}{N} (t_{n} + t_{3}) \left( \frac{N}{n} \right] + \tau \right].$

(22)

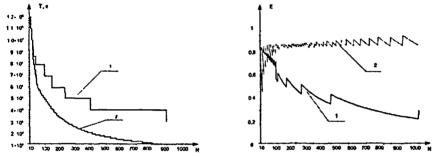

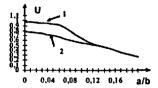

На рис 8 представлены сравнительные рафические зависимости времени решения (T) и эффективности распараллеливания (E) от различного числа процессоров (N). Здесь кривые, обозначенные цифрой 1, соответствуют мультипроцедурной организации вычислений; кривые, обозначенные цифрой 2, - структурно-процедурной организации вычислений.

При небольшом числе процессоров эффективность мультипроцедурной организации вычислений превосходит эффективность структурно-процедурных вычислений, но как только число процессоров системы достигнет количества вершин базового подграфа, происходит скачок производительности для структурно-процедурной организации вычислений. Легко заметить, что зависимость эффективности представляет собой пилообразную кривую, приближающуюся к линейной зависимости роста производительности при увеличении числа процессоров.

Рис. 8. Зависимости времени решения и эффективности от числа процессоров.

В третьей главе представлены разработанные средства описания структурнопроцедурных вычислений на основе языка программирования высокого уровня с неявным представлением параллелизма. В отличие от языков потоков данных предложено

ограничение: правило единственной подстановки действует в специальных конструкциях языка, описывающих вычислительные структуры, задаваемые пользователем. Кадр

языка соответствует совокупности арифметико-логических команд, выполняемых на

различных ЭП и контроллерах распределенной памяти, соединенных между собой в соответствии с информационной структурой алгоритма. В теле кадра может находиться

несколько операторов присваивания; программист не выделяет в них параллельные участки вычислений; в результате преобразования программы транслятором параллелизм,

содержащийся в описании ВС, извлекается из нее естественным образом на основании

взаимосвязей между данными. Описание кадра: CADR пате, P; END пате; где P - список

внутренних операторов кадра. Внутренние операторы кадра реализуются структурно,

внешние - процедурно. При этом обеспечивается биективное соответствие программе на

языке и граф-схемам.

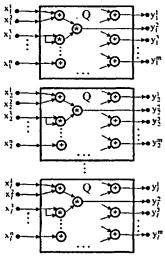

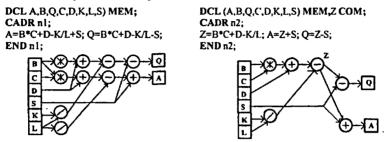

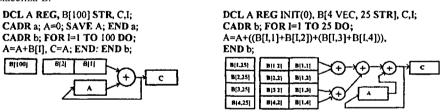

В предлагаемом языке переменные разделяются по способу хранения на мемориальные, коммутационные и регистровые. Мемориальной (МЕМ) переменной называется величина, хранящаяся в ячейке памяти и, следовательно, сохраняющая свое значение до очередного переприсваивания. Коммутационной переменной (СОМ) называется величина, служащая для описания каналов между элементами МВС, значения переменной данного типа недоступны пользователю. Введение переменной данного типа позволяет упростить графы вычислительных структур. На рис.9 приведены программы и эквивалентные им графы вычислительных структур, иллюстрирующие минимизацию оборудования при введении коммутационной переменной.

Рис. 9. Использование мемориальной и коммутационной переменных.

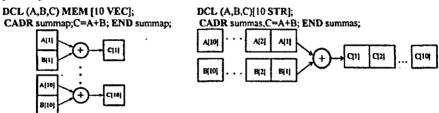

В данном языке массивы различаются по способу обработки на векторы и потоки. Потоками являются массивы, элементы которых могут быть обработаны только последовательно. Векторами являются массивы, элементы которых могут быть обработаны параллельно. На рис. 10 представлены программы, являющиеся граничными примерами извлечения параллелизма, и графы вычислительных структур, в которые они будут оттранслированы.

Рис. 10. Параллельное и последовательное сложение массивов.

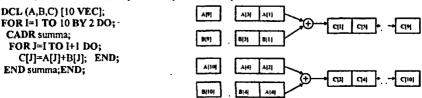

Все записи, находящиеся во внутреннем операторе цикла FOR, мультиплицируются в соответствии с параметрами цикла на вычислительную структуру для векторов или осуществляется периодическое поступление элементов массивов по заданной оператором цикла процедуре для потоков. Внешний по отношению к описанию вычислительной структуры оператор FOR осуществляет циклическое выполнение операторов, в том числе, и кадров, находящихся в теле цикла. На рис.11 представлен пример оператора цикла.

Семантика синтаксически одинаковых конструкций кадра определяется структурой данных, однозначно диктующих правило доступа к элементам массивов.

Рис. 11. Использование циклических операторов.

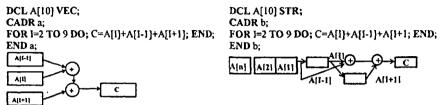

Если в одном кадре для вычисления переменной происходит обращение к нескольким элементам массива, то для вектора это означает определенным образом заданную коммутацию каналов распределенной памяти, а для потоков - запаздывание между элементами массива (неявно заданное использование регистровых переменных для буферизации). На рис.12 приведены программы и графы вычислительных структур, которые демонстрируют отличие индексации обращения к элементам потоков и массивов.

Рис.12. Обращение к элементам векторов и потоков.

Использование правила единственной подстановки в теле кадра приводит к трудностям при организации рекурсивных вычислений. Рассмотрим пример: пусть требуется осуществить сложение элементов массива. Эту задачу предложено решить наиболее эффективно с использованием регистровой переменной, для которой правило единственной подстановки не выполняется. На рис.13 представлены программы и эквивалентные им графы, производящие последовательное и параллельное суммирование элементов массива В.

Рис.13. Последовательное и параллельное сложение элементов массива.

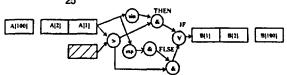

Для реализации ветвления в программах используется условный оператор IF. Семантика внешнего условного оператора совпадает с семантикой условных операторов процедурных языков программирования высокого уровня. Внутренний условный оператор выполняется следующим образом: группа операторов а и b, представляющих подграфы графа кадра, выполняется параллельно; результаты вычислений обеих групп поступают на переключатель, работа которого определяется логическим выражением q. Другими словами, внутренний условный оператор реализует структурный аналог условного перехода. Пример внутреннего условного оператора представлен на рис. 14.

Разработаны алгоритмы трансляции типовых конструкций языка и учитывающих особенности реализации структурных вычислений, разработаны алгоритмы компоновки графа кадра на макропроцессоры.

25

DCL (A,B) [100] STR; CADR b;FOR I=1 TO 100 DO; IF A[I]>0 THEN B[I]=sin(A[I]); ELSE B[I]=exp(A[I]\*\*2),END; END b;

Рис. 14. Структурный аналог условного перехода

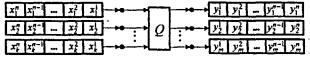

<u>В четвертой главе</u> на основании разработанных методов структурно-процедурных вычислений и средств описания программ разрабатывается технология индуктивных параллельных программ, обеспечивающая реализацию параллельных программ для различных конфигураций MBC.

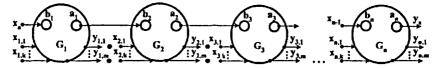

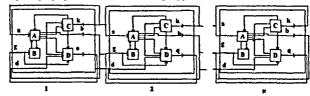

Для высокопроизводительных многопроцессорных систем с массовым параллелизмом необходимо обеспечить эффективную организацию многозадачного режима. При параллельном программировании задач на определенные аппаратные компоненты многопроцессорной системы со структурно-процедурной реализацией вычислений неизбежны простои в процессе реализации потока заданий. Очередное задание может быть отправлено на выполнение тогда и только тогда, когда свободны все аппаратные компоненты, требуемые заданию. Более совершенной является организация, когда каждая задача может быть решена практически на любом аппаратном ресурсе. Поскольку в кадр (рис.15) преобразуется кортеж базовых подграфов, то для структурно-процедурной организации вычислений можно синтезировать масштабируемые параллельные программы.

Рис.15. Исходный кадр.

Функции отображения базовых подграфов в одном слое могут в зависимости от степени распараллеливания реализовать-

ся как последовательно, так и параллельно. Функции отображения слоев реализуются исключительно последовательно.

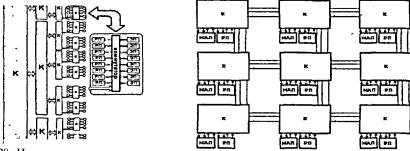

При увеличении аппаратного ресурса системы для решения задачи кадр можно естественным образом распараллелить. Граф кадра мультиплицируется столько раз, во сколько раз ресурс системы превышает ресурс, необходимый для структурной реализации графа Q, а также мультиплицируются каналы распределенной памяти, в которых хранятся исходные данные кадра и результаты. Формируется единый кадр (рис. 16), функциональный граф которого содержит несколько подграфов Q, что обеспечивает неизменность единой управляющей программы. Все элементы системы перестраиваются согласованно.

Поступившие задания рассматриваются планировщиком заданий, который реализует функции параллельных индуктивных программ и планирует загрузку МВС для различных вариантов распараллеливания задания.

Минимальное время отклика операционной системы, а, следовательно, и минимальное снижение эффективности решения задач на многопроцессорной системе обеспечивается при создании планировщика заданий по принципу разделения аппаратного ресурса. В этом случае заданию на время его выполнения выделяется неизменный фраг-

мент аппаратного ресурса, на котором задание выполняется практически независимо от других заданий, одновременно реализуемых в многопроцессорной системе.

Рис. 16. Распараллеливание кадра

Параллельные инлуктивные программы описываются четверкой <P<sub>o</sub>,X<sub>o</sub>,Fp,Fx>, где P<sub>o</sub> параллельная структурно-процедурная программа, решаемая на минимальном ресурсе Хо: Грфункция, ставящая в соо-

тветствие варианты распараллеливания задачи:  $P_1 = F_p(P_{t-1})$ ; Fx-функция, ставящая в соответствие варианты конфигурации MBC:  $X_i = F_X(X_{i-1})$ .

Алгоритм планировшика заданий представлен ниже.

- $1^{\circ}$ . Если пришло новое задание  $J_i$ , то оно ставится в очередь  $Q_i$ :  $SQ_i = SQ_i + 1$ ;  $Q_i[SQ_i] = J_i$ .

- $2^{\circ}$ . Если задание  $J_a$  в очереди активных заданий Qa завершилось, то перейти к  $3^{\circ}$ , иначе K 50

- $3^{\circ}$ . Переводится задание в выходную очередь  $Q_o$ :  $SQ_o = SQ_o + 1$ ,  $Q_i[SQ_o] = J_a$ ;  $SQ_a = SQ_a 1$ ,  $Q_a[SQ_a]=E.$

- ${\bf 4^0}$ . Множество базовых модулей  ${\bf L}({\bf J_a})$ , которые занимало задание  ${\bf J_a}$ , освобождается. Модифицируется свободный ресурс системы  $F: F = F \cup L(J_2)$ .  $5^{\circ}$ . j=1.

- 6°. Отбирается ресурс, удовлетворяющий требованиям j-го задания во входной очереди G=Q<sub>[j]</sub>: L(G)={ $l \mid F(l) \& \sim Ra(G)\& Sa(l) \& Rc(G) < Sc(l)$ }, где Sa(l) - характеристики l-го модуля системы, Sc(I) •• описание связей *l-го* блока системы. Если m=M(L(G))>0, то перейти к  $7^{0}$ , иначе к  $8^{0}$ . M(L(G)) - мошность множества L(G). m - степень распараллеливания (число базовых модулей для G).

- 7°. Задание снимается с входной очереди Q,[i]=E.

- $8^{\circ}$ , Модифицируется свободный ресурс F = F / L(G).

- $9^{0}$ . Инициализируется программа Pc(G,m), по окончании которой задание ставится в очередь активных заданий:  $SQ_a = SQ_a + 1$ ,  $Q_a[SQ_a] = G$ .

- 10°. i=i+1. Если SQ<sub>3</sub>>j, то перейти к 6°, иначе к 11°.

- 110. Просматривается очередь выходных заданий. Если к заданию с поступил запрос от пользователя, то задача пересылается пользователю и исключается из выходной очереди:  $SQ_0 = SQ_0 - 1$ ,  $Q_0[SQ_0] = E$ .

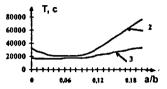

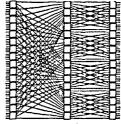

В диссертации также разработаны алгоритмы планировщика заданий с учетом ограничений топологии коммутационной структуры МВС, приоритетов и других дескрипторов параллельных заданий. Анализ эффективности планировщика заданий проводился по четырем параметрам: коэффициенту использования оборудования U, степени распараллеливания задачи R, доле времени вычислений C (отношение времени исполнения задачи к общему времени прохождения задачи) и времени прохождения потока заданий

T (рис.17). При проведении вычислительного эксперимента интенсивность обслуживания была зафиксирована и варьировалась интенсивность поступления. Интенсивность поступления b=l/t, t - среднее время между заданиями. Интенсивность обслуживания  $a=l/t_p$ , где  $t_p$  - время решения задачи.

Рис. 17. Эффективность планировщика индуктивных заданий.

Здесь цифрой 1 помечены кривые, соответствующие потоку индуктивных заданий, цифрой 2 - кривые, соответствующие потоку заданий с фиксированной степенью распараллеливания. Анализируя полученные результаты, можно отметить следующее. Технология параллельных индуктивных заданий позволяет существенно повысить загрузку оборудования системы и, следовательно, уменьшить стоимость решения задачи. Причем, для коммутационных сетей с меньшими возможностями по организации связей преимущество индуктивных параллельных заданий будет больше. Так, для плотно поступаюших заданий для коммутационной сети, построенной по полному графу, выигрыш в коэффициенте использования оборудования для индуктивных заданий составляет 20-25%; для коммутационной сети, построенной по графу типа "бинарное дерево" - 40-43%. При этом коэффициент использования оборудования для потока индуктивных заданий снижается незначительно. Для коммутационной сети по полному графу коэффициент использования оборудования для индуктивных заданий равен 0,97, для идеальных индуктивных заданий коэффициент использования оборудования равен 0,97, для коммутационной сети, построенной по графу типа "бинарное дерево" - 0,94. Примерно такие же соотношения имеют место для времени прохождения потока заданий T.

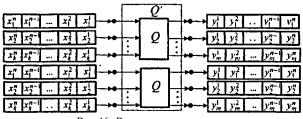

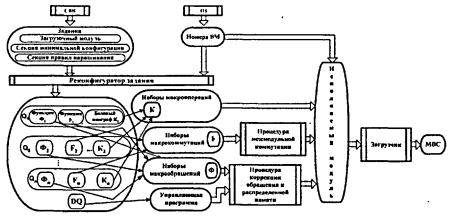

Одним из важнейших компонентов операционной системы, поддерживающих обработку потока параллельных индуктивных заданий, является разработанная в диссертации система посттрансляции, структура которой представлена на рис. 18.

Исходными данными для системы посттрансляции являются: задание, сформулированное в терминах технологии индуктивных программ, и номера базовых модулей MBC, выделенных для решения задачи планировщиком заданий.

Задание представляет собой тройку: **<Z**, $M_0$ **Ж>**, Z -загрузочный модуль;  $M_0$  граф минимальной конфигурации вычислительного ресурса, необходимого для структурно-процедурного решения задачи; W— секция правил наращивания графа конфигурации вычислительного ресурса при увеличении степени распараллеливания задачи. Задание должно быть запрограммировано в соответствии с технологией индуктивных параллельных программ. Показано, что в кадр преобразуется функционально-регулярный подграф задачи  $K_i$ = $F_i$ ( $\Phi_i$ (g)), где  $K_i$ -базовый подграф, который тиражируется для параллельного и последовательного выполнения;  $F_i$ - правило наращивания базового подграфа при параллельной реализации,  $\Phi_i$ - правило наращивания базового подграфа при последовательной реализации. Можно сказать, что функции  $F_i$  соответствует коммутационная

Рис.18. Структура системы посттрансляции.

составляющая, функции  $\Phi_i$  - составляющая обращения к каналам распределенной памяти, реализуемая последовательно во времени. Множество базовых подграфов всех кадров  $K=\{K_1, K_2,...,K_n\}$  образует наборы макроопераций. Множество функций  $F=\{F_1,F_2,...,F_n\}$  образует набор макрокоммутаций. Множество функций  $\Phi=\{\Phi_1,\Phi_2,...,\Phi_n\}$  образует набор обращений каналам РП.

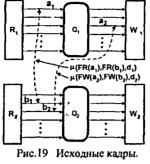

Если оборудования МВС достаточно для того, чтобы обеспечить максимальное распараллеливание не только в кадре  $K_{\mathbf{b}}$  но и в кадре  $K_{\mathbf{b}}$  который непосредственно связан с кадром  $K_i$  (расположен с ним на одном уровне графа кадров  $G_K$  или на смежных ярусах), то компоненты кадров  $K_i$  и  $K_i$  могут объединяться, образуя единый кадр K. Подобное объединение можно описать с помощью операции параллельного соединения. Для результирующего кадра формируются единый узел чтения и единый узел записи. При формировании объединенного кортежа функций чтения  $FR^{\bullet}$  в него включаются все функции, принадлежащие кортежу  $FR_{\mathbf{p}}$  а также те элементы кортежа  $FR_{\mathbf{p}}$  которые не состоят в отношении информационной зависимости с элементами кортежа функций чтения  $FR_{l}$  и с элементами кортежа функций записи  $FW_{l}$ . Здесь и далее будем говорить, что две функции fи  $\psi$  информационно зависимы, если для всей области их определения  $t \in [t_1, t_2]$ наблюдается равенство получаемых информационных вершин, формируемых выражениями f(t) и  $\psi(t+\Delta)$ , где  $\Delta$  - константа. В этом случае говорится о том, что существует отношение информационной зависимости  $\mu(f, \psi, \Delta)$ . Подобная зависимость может быть легко реализована с помощью элементов задержки, при этом дуги а и в, начало или конец которых связаны с функциями f и  $\psi$ , связаны отношением  $\psi$ (a, b,  $\Delta$ ). Причем, если в отношении Ууказана входная дуга, то с функцией чтения связано начало дуги, а если выходная, то с функцией записи связан конец дуги. Аналогично формируется кортеж функций чтения объединенного узла записи. Исходные кадры показаны на рис.19. Здесь функция чтения, соответствующая источнику дуги  $a_{l}$ , находится в отношении  $\mu$  с функцией чтения, соответствующей началу дуги  $b_l$ , а функция записи, соответствующая концу дуги  $a_3$ , находится в отношении  $\mu$ с функцией чтения, соответствующей началу дуги  $b_2$ . Данные дуги модернизируются: изменяется источник дуги, и на дугу включается бу-

Рис.21. Свертка кадров

фер с соответствующей задержкой операндов. Результат объединения кадров представлен на рис.20.

Если оборудование системы не позволяет реализовать кадр K даже для минимальной степени распараллеливания, то такой кадр необходимо разделить на два кадра:  $K_1 = (R_1, Q_1, W_1)$  и  $K_2 = (R_2, Q_2, W_2)$ , которые выполняются последовательно. Операция разъединения позволяет лля некоторого подграфа *VO<sub>1</sub>* С*VO* получить кадровую структуру, которая может быть реализована в МВС. Область определения функций чтения и функций записи в полученных в результате выполнения данной операции двух кадрах совпадает с областью определения функций исходного кадра. Если в результате выполнения множества операций разъединения оказывается, что существуют два кадра  $K_1$  и  $K_2$ , функциональные графы которых  $O_1$  и  $O_2$  и данные кадры расположены на одном уровне графа кадров, либо непосредственно связаны, то кадры  $K_1$  и  $K_2$ можно соединить последовательно, используя для этого операцию свертки (рис.21). При выполнении операции свертки размеры буферов, включаемых на дуги, находящиеся в исходных кадрах в отношении Д умножаются на величину  $N_1$  - размер информационного потока первого кадра. Операция свертки некоммутативна.

Программная реализация функций индуктивных программ содержит секцию описания графа минимальной конфигурации базового ресурса  $M_0$  и секцию правил наращивания ресурса. Описание графа минимальной кон-

фигурации представляет собой совокупность описания переменных, внешних связей графа и связей блоков. Предполагается возможность описания блоков по иерархическому принципу. Пример описания графа минимальной конфигурации приведен ниже.

Секция правил наращивания ресурса представляется следующим образом. В начале следует оператор описания переменных, задействованных в программе. Далее следуют операторы описания присвоения входных/выходных переменных графа минимальной конфигурации друг другу в зависимости от значения степени распараллеливания \_Par (специальное служебное имя) Кроме оператора присваивания в секции могут находитьдиться условные операторы и операторы организации циклов. Пример описания графа минимальной конфигурации представлен на рис.22, секций наращивания - на рис 23, 24.

BEGIN Graph;

DCL a 18, g 3, d.4, k:18, b:4, q·3,

ca·10, cd 2, ac:5,acd 8,ad 1,ab 4,ba 6;

INPUT (a,g,d);

OUTPUT (k,b,q);

A(IN(a,ca,ba),OUT(ac,acd,b,ad,ab),)

B (IN (ab,g); OUT(ba); );

C (IN (acd,ac); OUT(cd), );

D(IN(ad,acd,d);OUT(q,g););

END Graph;

Рис.22. Пример графа минимальной конфигурации.

DCL k; FOR i=0 TO \_Par-1 DO; k=cadd(i,-1,\_Par-1); a[i]:=k[k],b[i]:=q[k]; g[i]:=d[k]; END;END PROGRAM.

Рис.23. Пример секции линейного нарашивания.

DCL a,b,i,j,k,l;

\_Par=a-b; a:=log(\_Par)/log2,b=a;

IF a - int(a) = 0 BREAK;

a:=a+1; b:=N/a;

IF b - int(b) = 0 BREAK; b:=b-1; a:=N/b,c:=b/4;

FOR k=1 TO a DO; n:=cadd(k,-1,a); s:=0;

FOR j=1 TO b DO;

FOR i=1 TO 4 DO; s:=s+1; l.=s mod 4; m:=s / 4; Wi[k,j,i].=Wo[n,l,m];

END; END; END;

END PROGRAM.

Рис.24. Пример секций наращивания ресурса в соответствии с косвенным бинарным графом для процедуры БПФ.

<u>В пятой главе</u> представлены разработанные программно-аппаратные средства, поддерживающие структурно-процедурные вычисления на уровне элементной базы.

Для обеспечения высокой производительности архитектура МВС должна воплощать основные принципы построения системы на всех уровнях, включая уровень элементной базы. С учетом этого в основу создания элементной базы для многопроцессорных вычислительных систем с массовым параллелизмом положены следующие принципы: унифицируемость; минимальная номенклатура; аппаратная поддержка синхронизации вычислений; аппаратная реализация системы команд; совмещение процессов обработки и передачи данных.

Для МВС ПА основными функциональными устройствами являются: макропроцессор, блок распределенной памяти, макрокоммутатор.

Функция обработки информации осуществляется в макропроцессоре (МАП), который содержит группу элементарных процессоров и коммутационную структуру, соединяющую  $\Theta$ П по полному графу.

Макропроцессор предназначен для построения высокопараллельных процессорных полей со структурной реализацией крупных операций (макроопераций) графов вычислительного процесса. Разработаны и созданы различные варианты МАП на основе ПЛИСтехнологии, реализующие вычисления в знакоразрядном и стандартном кодах.

В диссертации разработаны средства программирования макроопераций, представляющих собой программно-неделимую совокупность команд элементарных процессоров, образующих структурно-реализуемую функционально законченную математическую операцию. Директива описания макроопераций имеет следующий формат.

Macrooperation ими (in список формальных параметров входов, processors список формальных имен ЭП, out список формальных параметров выходов) Совокупность команд ЭП, Endmacro;