Разработка методов и алгоритмов проектирования тонкопленочных микросборок высокой интеграции

- Автор:

Спирин, Владимир Георгиевич

- Шифр специальности:

05.27.05

- Научная степень:

Кандидатская

- Год защиты:

1999

- Место защиты:

Б. м.

- Количество страниц:

142 с.

Стоимость:

700 р.499 руб.

ОГЛАВЛЕНИЕ

Введение

1 Проблемы создания микросборок высокой интеграции.

Задачи исследований

1.1 Основные направления разработок микроэлектронной аппаратуры высокой интеграции

1.2 Погрешности ТПР, методы их расчета и компенсации

1.3 Основные конструкции ТПР и способы изготовления платы МСБ

1.4 Методы анализа производственных погрешностей ТПР

1.5 Основные принципы проектирования МСБ

1.6 Цель и задачи исследований

2 Методы оценки погрешностей тонкопленочных элементов

2.1 Математические модели сопротивления и производственной погрешности ТПР

2.2 Анализ погрешностей суммы, разности, произведения и отношения двух ТПР, изготовленных на одной плате

2.3 Разработка тестовой схемы для определения производственных погрешностей сопротивления ТПР

2.4 Алгоритмы оценки производственный погрешностей

тонкопленочных элементов

2.5 Алгоритмы оценки инструментальных погрешностей

сопротивления ТПР

Выводы

3 Конструктивно-технологические способы повышения интеграции тонкопленочных микросборок

3.1 Модификация первого способа двойной фотолитографии

3.2 Способы компенсации систематических погрешностей сопротивления ТПР

3.3 Расчет стационарного теплового режима МСБ

3.4 Требования к технологическому процессу и оборудованию

для изготовления тонкопленочных МСБ высокой интеграции

Выводы

4 Алгоритмы расчета, проектирование и экспериментальные исследования тонкопленочных МСБ высокой интеграции

4.1 Алгоритм выбора конструкции кондуктивного тракта для компонента

4.2 Особенности проектирования топологии платы МСБ

4.3 Разработка конструкции плат МСБ для акселерометра

4.4 Экспериментальная оценка производственных и

инструментальных погрешностей ТПР

4.5 Экспериментальное определение теплового сопротивления кондуктивного тракта

Выводы

Заключение

Благодарности

Перечень принятых сокращений

Перечень принятых условных обозначений

Список литературы

Введение

Актуальность теш. Создание высококачественных надежных радиоэлектронных средств с использованием последних достижений микроэлектроники при минимальных производственных затратах стало возможным благодаря современной технологии микроэлектронной аппаратуры (МЗА), основной конструктивной единицей которой является микросборка (МСБ) til. Основным направлением развития микроэлектроники является повышение степени интеграции компонентов и МОЕ [23,

Проблемы миниатюризации различных радиоэлектронных устройств рассмотрены в [70]. Актуальность миниатюризации аналоговых устройств и их компонентов вызвана скопившейся и продолжающей расти диспропорцией массогабаритных параметров этих устройств в сравнении с цифровыми устройствами. Эта диспропорция в миниатюризации различных составных частей МЗА обусловлена как схемотехническими решениями, так и конструкторско-технологическими.

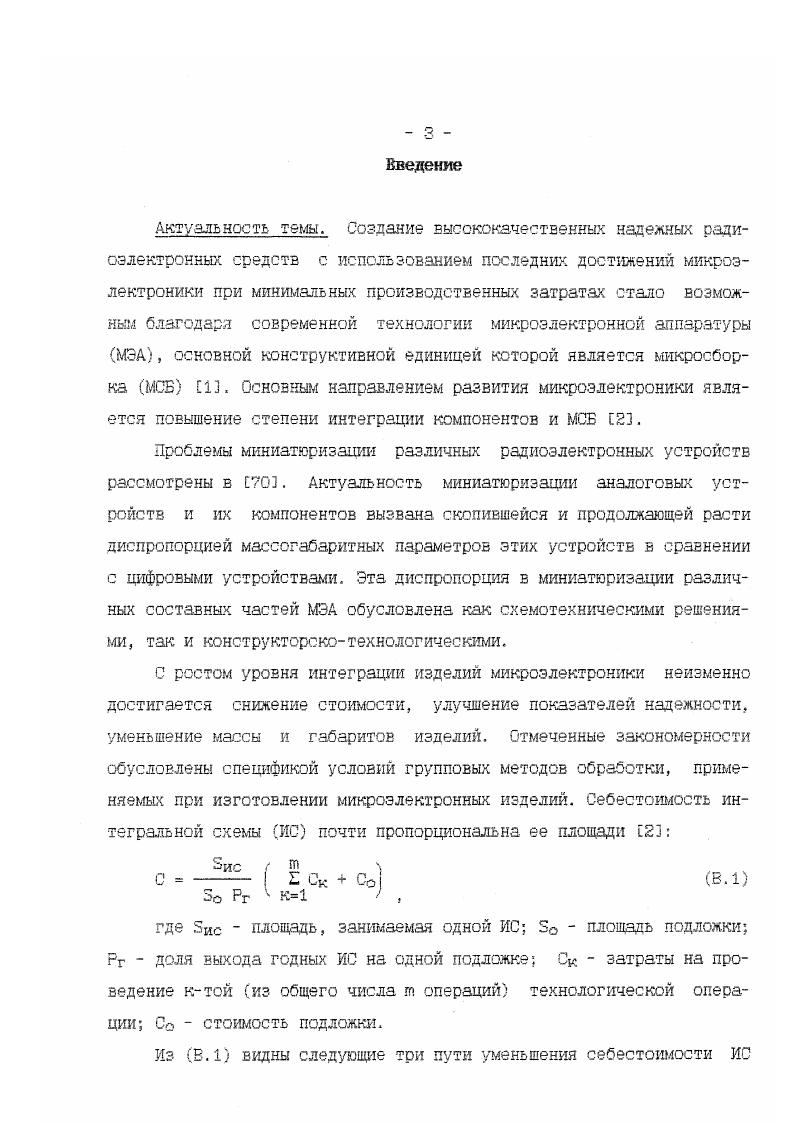

С ростом уровня интеграции изделий микроэлектроники неизменно достигается снижение стоимости, улучшение показателей надежности, уменьшение массы и габаритов изделий. Отмеченные закономерности обусловлены спецификой условий групповых методов обработки, применяемых при изготовлении микроэлектронных изделий. Себестоимость интегральной схемы (МО) почти пропорциональна ее площади [23:

где Зис - площадь, занимаемая одной ИС; Б0 - площадь подложки? Рг - доля выхода годных ИС на одной подложке? 0К ~ затраты на проведение к-той (из общего числа гп операций) технологической операции; Со - СТОИМОСТЬ подложки.

Из (В.1) видны следующие три пути уменьшения себестоимости ИС

(В.1)

при неизменной площади So подложки. Во-первых, стоимость ИС уменьшается, если уменьшается площадь ИС 5ИС, так как при этом увеличивается число ИС, размещаемых на одной подложке. Последнее обеспечивается масштабным уменьшением геометрических размеров элементов, так как при росте плотности упаковки себестоимость изготовления платы L Ск изменяется незначительно или вообще не изменяется (Е Ск % const). На практике выгодно не только добиться увеличения плотности размещения элементов, но и увеличить интеграцию изделия микроэлектроники, Последнее достигается как увеличением плотности упаковки, так и площади, занимаемой ИС, Во-вторых, себестоимость ИС уменьшается при увеличении Р, то есть процента выхода годных ИС, изготавливаемых на одной подложке. В-третьих, себестоимость ИС уменьшается при снижении Е Ск, то есть затрат на проведение технологического процесса ИС.

Одним из основных элементов МСБ, который влияет на степень интеграции, является тонкопленочный резистор (ТПР'), В настоящее время хорошо отработана технология изготовления ТПР с минимальными размерами 0,2 мм. МСБ, содержащие резисторы с линейными размерами 0,05, 0,1 мм, имеют недостаточный для практики выход годных [303.

Применяемые на практике методы расчетов ТПР не позволяют уменьшать их размеры в связи с малой допустимой рассеиваемой мощностью, которая, как правило, не превышает 35 мВт/мм2. Методы расчетов тепловых режимов МСБ [73, 743 достаточно громоздки и неудобны для инженера-конструктора даже при использовании средств вычислительной техники. Кроме того, эти методы предназначены для расчета определенных конструкций МСБ и не решают вопросов выбора материала и конструкции платы, а также выбора соединительных материалов, предназначенных для соединения компонентов с платой и платы с- осно-

Систематические погрешности размеров ТПР находят, решая систему уравнений:

1-і + ДД

И. = р

Ьі - ДЬС + Д1с

(1.8)

ІЗ + Мс

КЗ = р

Решение находят для частного случая, характерного для выбранных размеров ТПР тестовой схемы. Величины систематических погрешностей размеров ТПР определяются по следующим формулам:

0ДК1 - 0,5К2 0,1152 - 0,5КЗ

ДЬС =

Р.1 - Р.2 ‘ КЗ

Алгоритм этого решения не может быть использован для других размеров тестовых элементов без дополнительных преобразований.

Расчет контактного сопротивления в работе С221 производится по очень трудоемкому алгоритму. Недостатком этого расчета является низкая точность, так как выбранные размеры тестовых резисторов практически нечувствительны к погрешности контактного сопротивления, ВВИДУ больших коэффициентов Форш (Кф > 0,2). Это следует из того, что как показывает практика погрешность контактного сопротивления оказывает существенное влияние только на низкоомные резисторы (К < 20 Ом). Учитывая, что К = р Кф, надо, в зависимости от исследуемого значения р, соответствующим образом выбирать Кф тестового резистора. Резисторы с Кф = 0,2 могут быть чувствительны к погрешности контактного сопротивления только при малых р (р < 100 0м/а), что и следует из результатов экспериментальных данных работы [221.

В работе [2] приводится алгоритм расчета как систематических таї-; и случайных погрешностей размеров ТПР. Оценка производственных

Рекомендуемые диссертации данного раздела

| Название работы | Автор | Дата защиты |

|---|---|---|

| Исследование и разработка методов и устройств для уменьшения ошибки многолучевости в навигационном приемнике, реализуемом с использованием специализированной СБИС | Жданов, Алексей Владиславович | 1998 |

| Исследование и разработка методов автоматизированного конструирования модульных устройств КВЧ | Лейбман, Алексей Михайлович | 1998 |

| Устройства формирования и обработки ШПС для использования в радиосети связи | Мельник, Сергей Владиславович | 1998 |